Solstice-TDS TimeTable module

While translating ATPG patterns (WGL and STIL formats) is a push-button operation using Solstice-TDS, converting Verilog simulation output (VCD and EVCD) to a tester format involves a process called cyclization. This process creates cycle-based timing from the event-based VCD/EVCD file.

With Solstice TimeTable, signals, directions, test period, per-pin timing, and ATE format are all automatically detected and filled in.

- Auto-Fill Signals, Directions, and ATE Format. Just from reading in the VCD/EVCD file, TimeTable can extract and populate the timing table with signal names, their directions, and the detected waveform, hence, ATE format (eg, NRZ, R0, R1, etc).

- Auto-Detect Cycle Length. TimeTable can detect the most regulated clock waveform in the source VCD/EVCD file and fills in the cycle length appropriate for cyclization. If there are more than one found, TimeTable will present the list of periods for the user to choose from.

- Auto-Detect Per-pin Timing. TimeTable performs a comprehensive analysis of all events in the VCD/EVCD file and constructs ATE-waveform and timing that conform to the target ATE's rules. This feature is key in ensuring all intended behaviors in the simulation event are preserved. Without it, tests could fail good parts, or worse, bad parts are being passed (which is often the case when tools and engineers short cut pattern generation step).

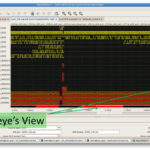

- Comprehensive viewing and resolving issues of complex timing. All timing constructed are presented with statistics of occurences, and each of which can be examined in a waveform viewer by a simple mouse click. This prevents design intents being overlooked, and potential issues getting into the final test patterns, which will be expensive to debug.

- Cross-departmental Usability. With all complex tasks automated, TimeTable can be used by design verification, product engineering, and/or test engineering. Whichever test development methodology you use, TimeTable is the right tool for the right job: redisocver design timing fast and accurately without manual intervention.