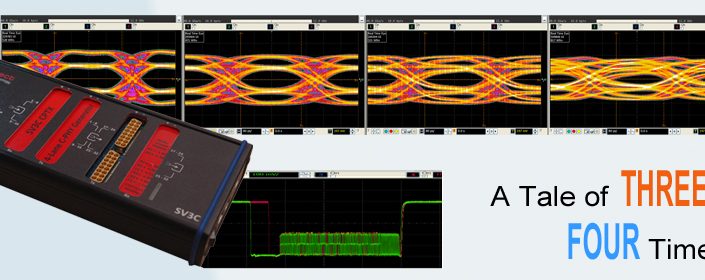

業界をリードする4レーンMIPI C-PHYジェネレータ

SV3C-CPTX C-PHYジェネレータは、ポータブルで高性能な機器で、MIPI C-PHYレシーバポートの動作と検証を可能にします。 C-PHYジェネレータは、トラフィックを生成し、完全なデータレートに対応することができるため、レシーバの感度性能とスキュー/ジッタ耐性を深く理解できるようにするアナログパラメータ制御を備えています。

C-PHY Generatorは、多目的なIntrospect ESPソフトウェア環境を使用して動作します。 この環境では、電圧感度やワイヤースキュー耐性などのレシーバーテストを自動化できます。 この環境には、カラーバーやアクティブなイメージフレームのような完全なDSIまたはCSIパケットの生成を可能にするMIPIパターンコンパイラツールも含まれています。

主な利点

- 任意レート動作およびグローバルタイミングパラメータ制御

- <1 ps分解能のワイヤースキューインジェクション

- ワイヤーごとの電圧レベル制御

- ワイヤーごとのLP生成

- 非常に直感的なPython言語に基づく最先端のプログラミング環境

- 再構成可能なプロトコルのカスタマイズ(要望に応じて)

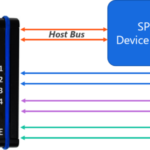

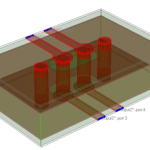

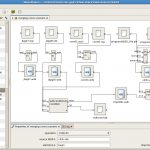

ブロック図と信号生成の概念

SV3C CPTXは、4つのC-PHYレーンでLPとHSの両方のデータストリームを同時に作成できるパターンジェネレータです。 パターンジェネレータアーキテクチャは、LPイベント、HSイベント、およびグローバルタイミングイベントをワイヤ単位で個別に制御します。 したがって、シームレスなソフトウェア環境内から準拠したCSI-2パケットおよびビデオフレームを生成するのに十分な汎用性を持ちながら、AWGソリューションと同様に完全な電気テストカバレッジを提供します。

SV3C CPTX内のHSジェネレータには、専用のハードウェアC-PHYマッパおよびエンコーダ回路が組み込まれています。 これにより、非常に使いやすくなります。 例えば、パケット伝送を定義する場合、ユーザは(自分が望む場合を除いて)ワイヤ状態または遷移を手動で構築する必要はなく、16ビットの整数ペイロードデータを定義するだけでよい。

バーストモードパケット生成およびグローバルタイミング制御

SV3C CPTXはパケット伝送のあらゆる側面を、完全にシームレスに定義することを可能にします。 ペイロードデータは、C-PHYプロトコルマッピングまたはエンコーディング技術の知識がなくても、ペイロードのデジタルデータと同様に宣言されます。 また、準拠したC-PHY PRBSパターンで物理層テストが必要な場合は、Introspect ESPソフトウェアで迅速に選択できるように、そのような刺激ファイルがツールにあらかじめ組み込まれています。

同様に、SV3C CPTXはグローバルタイミングパラメータを制御することができ、これはさまざまな動作条件でHS受信機の機能を自動的に確認するのに便利です。 基本的なcphyPatternコンポーネントは、HS送信を開始し終了するタイミングを変更するためのpreBeginNumUIやpostNumUIなどのパラメータを定義します。 同様に、lp000Durationのようなタイミングパラメータは、受信機をバーストモードで試験するときの準備(終了可能化)期間を変更することを可能にする。

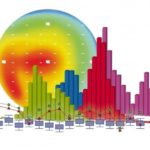

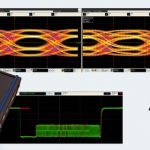

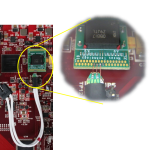

アナログ・パラメータ・コントロールのフル・スイート

C-PHY規格で要求されるように、SV3C CPTXジェネレータの各ワイヤは3レベルのシングルエンド波形を生成します。 波形のスパン(すなわち、低レベルから高レベルまでの距離)は電圧振幅と定義され、C-PHY規格のVOD仕様に対応する。 さらに、受信機がストレスを受けたアイテストを可能にするために、ジェネレータは、ソフトウェアコマンドに基づいて波形全体(低、中、高レベル)が上下にシフトするコモンモード制御を備えています。 同様に、すべてのLPレベルは、細かい分解能でプログラム可能です。 そのようなプログラム可能性は、C-PHYにおけるLP / HS相互作用に関連する様々な試験を可能にするために必要である。 最後に、ワイヤHS電圧(ミッドレベル制御)の対称性を操作し、各ワイヤに個別にジッタを注入するための高度なオプションがあります。これらはすべて受信機に見られる差動目を閉じるのに役立ちます。