Solstice

プレシリコン・パタン検証ツールで、設計者とテストエンジニアが同じ環境下で作業できます

SCANやファンクションパタン(ATPG, BIST, STIL, WGL, 各種ATEプラットフォーム, IPコアベンダー)を、設計者のDUTモデルで、検証することができます。 初期段階で問題を抽出することによって、多大なコストをかけずに解決することができます。

共通の問題

- パタン変換やパタン統合することによって、設計者が当初想定していることから変更されてしまう

- 設計者チームは、パタン品質のフィードバックを待つか、テスト技術者チームに依存しなければならない

- 設計者とテストエンジニアの不正確なコミュニケーションに起因して、開発サイクルが長くなる

- パタンデバッグ時に、設計とテストのデータ相関をとることが自動化されていない

- サイクルベースのパターンを印加するとDUTが誤った動作をする

- ATE間の変換誤差がある 等

Solsticeは環境を変えます

Solsticeは、設計とテストの相互作用の方法を変更します。設計者チームは、自身のテストプラットフォームを生成、検証でき、Solsticeの検証済みシミュレーションフローを再利用することができます。実行可能なフローダイアグラムで、パターン変換や特定ATEのパタンを設計シミュレーション環境で検証できます。テストエンジニアは、実際のデバイスが無い段階でテストパターンの検証を開始できます。問題のレポートや画面のスクリーンショットを送らなくても、テスト・エンジニアチームは、フェイル箇所と原因を設計者と共有することができ、設計者は同じシミュレーション環境下で問題点を再現することができます。

「シナリオ・キャンバス」は実行フロー・ベース

Solsticeはポイント&クリックの簡単操作です。クリックして、パターン検証操作(pv)を挿入します

- STILファイルをドラッグし、Solsticeが自動連結します

- Runをクリックします!

Solsticeインターフェース

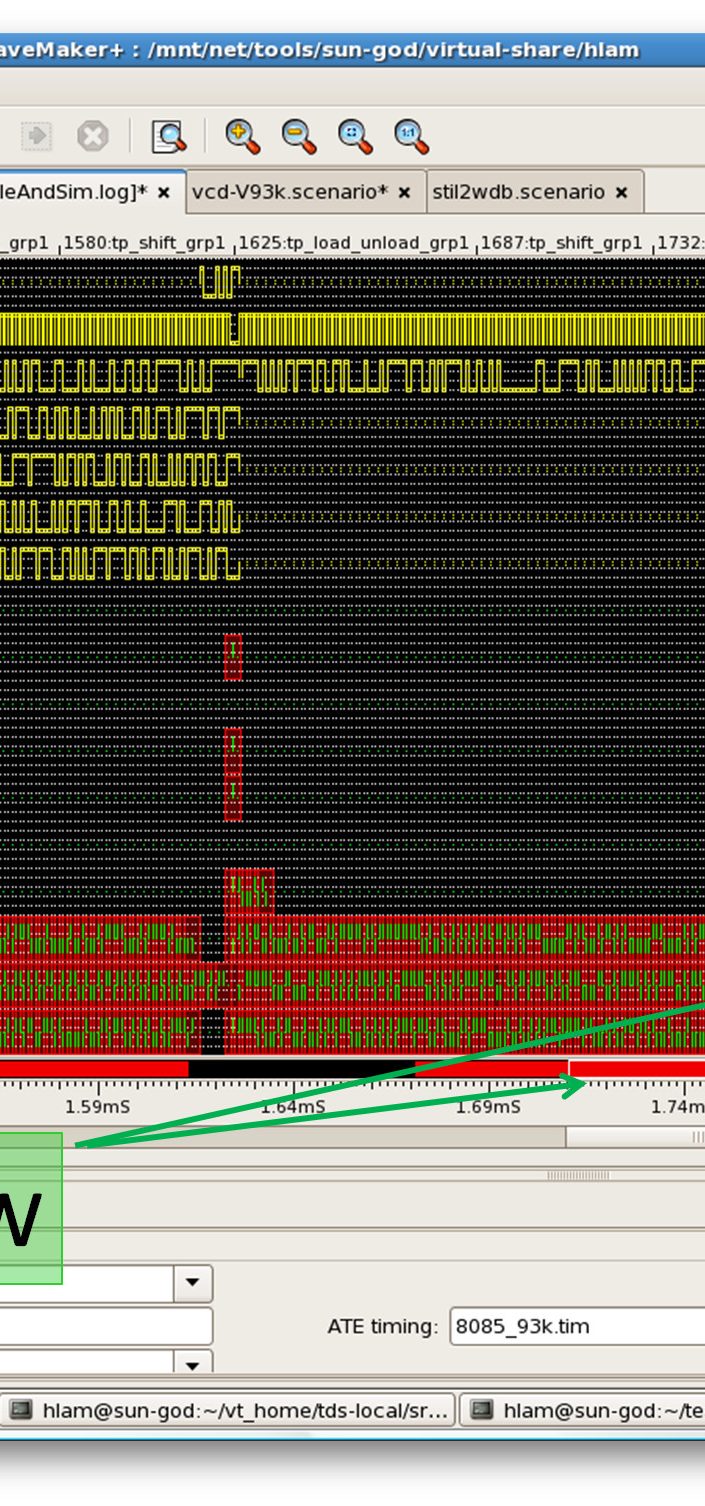

1つの環境で、表示設計とテスト・データは、チーム・コミュニケーションを最適化します。そして、テスター・サイクルで、スキャン・セル名、スキャン・サイクルとシミュレーション・タイムスタンプでATEピンの変化の正確な相関関係を明らかにします。ATEタイム-セット名は、デザインtestbenchで、イベント・シーケンスをコード化してマップされます。

オンザフライ故障解析

主要な論理シミュレータとのSolsticeのシームレス・インテグレーションは、ATEパターンの期待値と、DUTの間の相違を即時表示します。Solsticeの強力なグラフィカル・ユーザ・インタフェース(GUI)は、デザイン・タイムスタンプ対テスター・サイクルのストローブ配置とタイプ(エッジ、または、ウィンドウ)(フェイルの性質)と相関関係を表示します。

故障情報のログは、カスタムメイドのシミュレーション環境でも、後処理目的で利用可能です。エラー・ログファイルをSolsticeの波形エディタにドラッグ&ドロップします。

EDAのエラーフォーマット(シミュレータ、または、ATPGツールから)とSTDF(ATE標準データ・フェイル・フォーマット)を、サポートします。

その場で波形編集

シミュレーションは、マウスをクリックすることでSolstice環境で、停止できます。Edit-in-Place機能は、タイミングとパターン調節が可能で、Verilog再コンパイルなしでシミュレーションを再開します。これは、テスト、または、設計の検証チームによって迅速なトラブルシューティングを有効にします。

「バーズアイ」ビュー

プロトタイプでは数十億サイクルで、何千ものピンでフェイルし、多くはスキャン・チェーンに埋もれています。フェイルの特定のシグネチャを見ることは、デザインの特定地域、または、テストパターンの領域を探すヒントになります。デザイン、または、テストで、Solsticeのスマートな波形ズーミング機能(最新のデータベース・ランダムアクセス技法)で、フェイルがチェッカ・パターンか、コーナーか、対称形かといったの外観を示します。

「バーズアイ」ビューも、フェイル領域の集中部を表示します。

ATE固有パタンを検証

STILファイルを検証するのと同様に、ATE固有のパターンも、同じ方法で操作できます。下のスクリーンショットで、一組のアドバンテストV93000ファイルが検証されています。一組のピン、タイミングとバイナリパターン・ファイルです。タイミング・セット番号、等式セット番号とスペック・セット番号は、V93000ファイルで必要とする3つの付加パラメータです。これらはSolsticeのPropertySheetで、入力でき、残りは上のSTIL例と同じです。