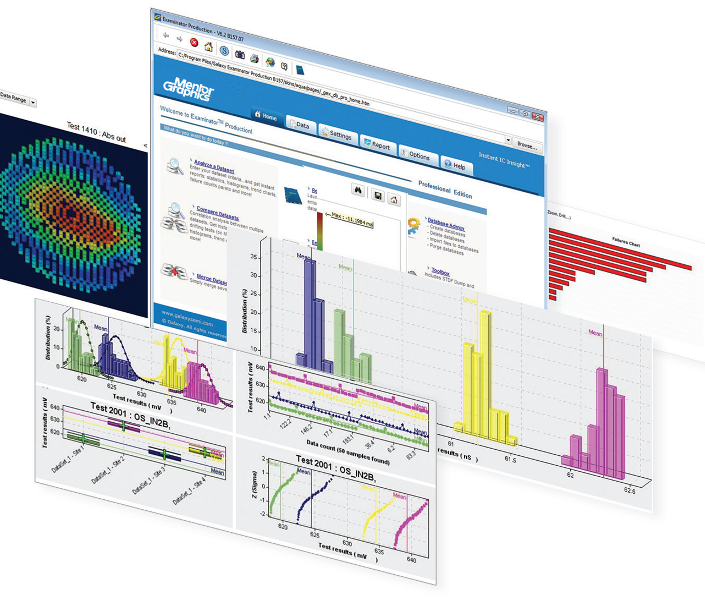

Examinator-Pro

Examinator-ProTMとは?

Examinator-ProTM(EXAMINe+translATORの造語)は、IC LSIテスト・エンジニアまたは半導体プロダクト・エンジニアが、標準テストデータ形式のSTDF (ATDF) やVerigy (Agilent) GDF、e-Test (WATやPCM)、CSV、RosettaNetなどといった標準的な半導体テストデータファイルを使って、デバイスの特性評価や生産モニタ、歩留り解析研究を可能にするソフトウェア・ソリューションです。

アプローチ

Examinator-ProTMは約20年の半導体テスト経験を持ったGalaxy社の設計者によって開発されたもので、複雑な解析ツールをマスターするための十分な時間を持てない今日のIC LSIテスト・エンジニアや半導体プロダクト・エンジニアのための最適ツールです。Galaxy社の目標は、Examinator-ProTMを“シングル・クリック”ソリューションにすることであり、それは数回のクリックにてユーザが望むレポートが得られることです。

ユーザは?

Galaxy社の数千ユーザの大半は、ファブレスやIDM、サブコン、テスタ会社のプロダクトエンジアやテストエンジア、プロセスエンジニアの方々です。通常、これらの方々は、デバイス出荷の初期段階で特性評価や歩留まり解析研究を行います。その後、生産が軌道に乗ると日々の生産実行のモニタリングを行います。これらに発生する問題を素早く解決するために、何百万のデータポイントや時間的なプレッシャーがあるとすれば、迅速なデータ解析は重要となります。Examinator-ProTMはそのご要求にお応えします。処理時間に関する比較を以下に示します。

記:精度を保証するために60MB以上のデータベースを基にしています。

データ解析:主な機能

- 必要となる以下の解析レポートが生成できます。

- 一般情報:ICテスタ、ロット、オペレータ情報

- 歩留まり情報:良品、不良品、再テスト品

- テスト・サマリ:テスト名、リミット、不良数、最小値、最大値、レンジ、 平均、シグマ、工程能力指数(CP、CPK)、スキューなど

- テスト・ヒストグラム:テスト分布のすばやい表示

- パラメトリック・テスト・ウェハマップ:プロセス問題を調査するための、ウェハのテスト傾向を解析します。

- ウェハマップ:生産でテストされたすべてのダイの時間情報、複数のウェハの重ね合わせや直接比較(ソフトビン、ハードビン、パラメトリック、…)

- 対話形式の2D/3Dチャート:ヒストグラムやトレンド、スキャッタ・プロット、ウェハマップ・チャートへのズーム・イン

- パラメトリック・トレンド・チャート:どのようにテスト結果が進展したかを見ます(再現性解析または生産トレンド)

- パレート・レポート:テストのCP、CPKやテスト不良、ソフトやハードビン

- データログ:データベースから生データの抽出

- 相関レポートやチャート、ボックス・プロット・ゲージR/R:AV、EV、R&R、PV、TV、…

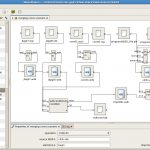

ICテスト時間短縮(TTR):主な機能

ICテスト時間短縮は、ICテスト安定性やICテスト相関を明らかにする必要があるために、非常に深いデータ解析と過去データ解析が要求されます。テストの再整理、修正、削除などのテスト時間短縮使命は、Examinator-ProTMによって迅速に達成できます。以下の包括的なレポートに即座にアクセスすることができます。

- テストの過去安定性と不良情報

- テスト間の相関

- ビン対テスト相関プロット

- その他

データレポーティング:主な機能

チームのメンバーや管理者とレビューするためのレポートやプレゼンテーション資料を作成するのに貴重な時間を費やす必要はありません。Examinator-ProTMでは、ワンクリックにて以下の標準的なファイルフォーマットのコンプリートレポートを作成します(第3社のソフトウェアは必要ありません)。

- ワード文書(.doc)

- パワーポイント・スライド(.ppt)

- PDFファイル(.pdf) * HTML文書(.htm)

- エクセル/CSV(.csv)

半導体生産性機能

Examinator-ProTMは、データ処理や他者との解析結果のコミュニケーションを容易にするための以下の機能を含んでいます。

- ブラウザベースGUI:すべてのアプリケーションは、WEB対応型です。特別なトレーニングを必要としません!

- スマートインポート:カレンダ・デート・フィルタイングにより、生産データの簡単な抽出が可能です。

- STDF、WAT、Verigy GDFなどのファイルを直接取り込み:データベースやコンバータを必要としません。

- データを他者とシェアするために、HTMLバインダ内の要点データをスナップショットやメモをとして保存できます。

- 自動化:タスク自動化を簡単にするビルトインスクリプト言語。

- ツールボックス:データファイルを編集やダンプ、またはコンバートするためのツール(STDFを含め、ATDF、Verigy GDF、WAT、PCM、PIP7C7などのフォーマットをサポート)

主な利点

- ユーザ調査によると、お客様は以下の点を評価されています。

- 迅速な既成レポート生成:迅速なデータ総覧のために、すべての一般的なレポートを同時に生成できること。

- 標準的なHTMLレポートフォーマット:製造業者と顧客との間、プロダクト・エンジニアとテスト・エンジニアの間、PCユーザとUNIXユーザとの間で、コミュニケーションが容易にできること。

- 比類ない使い易さ:トレーニングを必要としないために、即座の導入を可能にします。

- 多能:異なるテスタ・プラットフォームやデータフォーマットを幅広くサポートします。

測定システム分析 – ゲージスタディ

メーカのページに移動

ホワイトペーパー

多変数特性

「仮想再テスト」と対話的にデバイステストの制限を調整する方法

•仮説的なテスト限界による「what if」分析の実行方法

•潜在的な限界調整の影響を分析する方法

•新しい制限をテストプログラムにエクスポートする方法

メーカのページに移動

ドリフトをキャッチ? 詳細なチップ信頼性解析を実行する方法

- シフトテストのデータを整理する方法

- 時間と温度の変化を見る

- データを自動的にソートして、最悪の場合のシフトを特定する